# **EE 505** Lecture 12

### DAC Design

- DAC Architectures

- String DACs

Often this can be approximated by

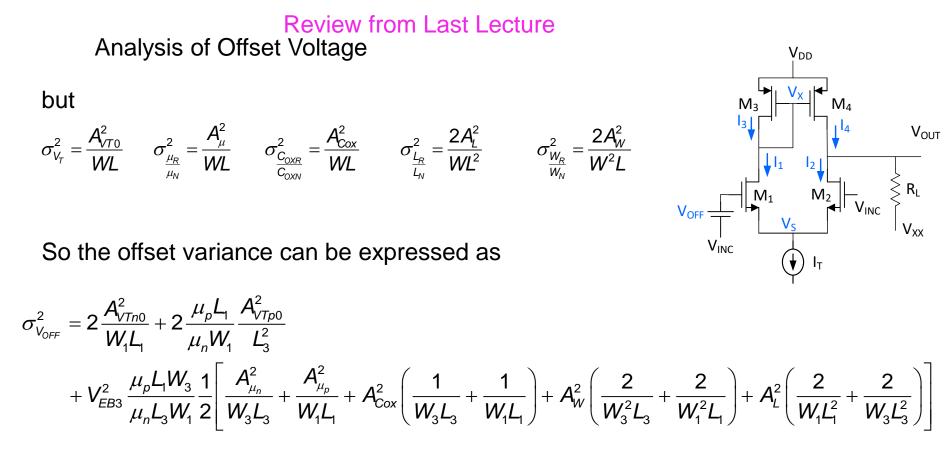

$$\sigma_{V_{OFF}}^{2} = 2\frac{A_{VTn0}^{2}}{W_{1}L_{1}} + 2\frac{\mu_{p}L_{1}}{\mu_{n}W_{1}}\frac{A_{VTp0}^{2}}{L_{3}^{2}} + V_{EB3}^{2}\frac{\mu_{p}L_{1}W_{3}}{\mu_{n}L_{3}W_{1}}\frac{1}{2}\left[\frac{A_{\mu_{n}}^{2}}{W_{3}L_{3}} + \frac{A_{\mu_{p}}^{2}}{W_{1}L_{1}} + A_{Cox}^{2}\left(\frac{1}{W_{3}L_{3}} + \frac{1}{W_{1}L_{1}}\right)\right]$$

Or even approximated by

$$\sigma_{V_{OFF}}^{2} = 2\frac{A_{VTn0}^{2}}{W_{1}L_{1}} + 2\frac{\mu_{p}L_{1}}{\mu_{n}W_{1}}\frac{A_{VTp0}^{2}}{L_{3}^{2}}$$

# Correspondingly: Review from Last Lecture

$$\sigma_{V_{OS}}^{2} = 2 \left[ \frac{A_{VTOn}^{2}}{W_{n}L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n}L_{p}^{2}} A_{VTOp}^{2} + \frac{V_{EBn}^{2}}{4} \left( \frac{1}{W_{n}L_{n}} A_{\mu_{n}}^{2} + \frac{1}{W_{p}L_{p}} A_{\mu_{p}}^{2} + A_{COX}^{2} \left[ \frac{1}{W_{n}L_{n}} + \frac{1}{W_{p}L_{p}} \right] \right) + 2A_{L}^{2} \left[ \frac{1}{W_{n}L_{n}^{2}} + \frac{1}{W_{p}L_{p}^{2}} \right] + A_{w}^{2} \left[ \frac{1}{L_{n}W_{n}^{2}} + \frac{1}{L_{p}W_{p}^{2}} \right] \right]$$

which again simplifies to

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTOn}^{2}}{W_{n}L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n}L_{p}^{2}} A_{VTOp}^{2} \right]$$

Note these offset voltage expressions are identical!

**Review from Last Lecture**

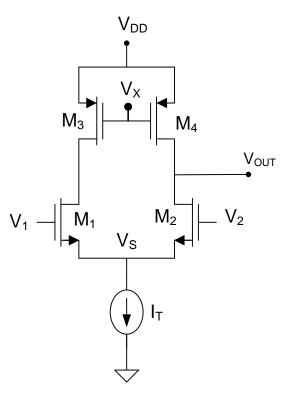

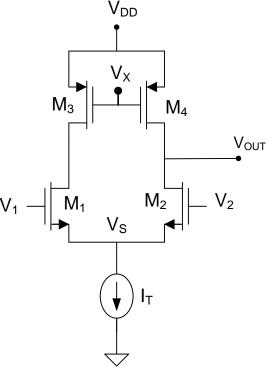

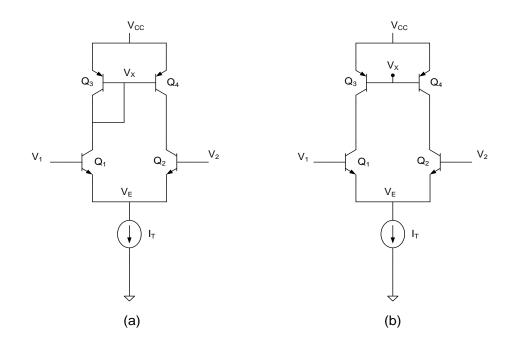

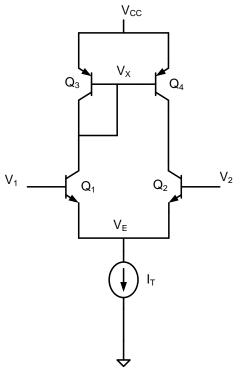

# **Random Offset Voltages** Example: Determine the 3 $\sigma$ value of the input offset voltage for

The MOS differential amplifier is

a)  $M_1$  and  $M_3$  are minimum-sized and

b) the area of  $M_1$  and  $M_3$  are 100 times minimum size

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTOn}^{2}}{W_{n}L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n}L_{p}^{2}} A_{VTOp}^{2} \right]$$

$$\sigma_{V_{OS}}^{2} \cong \frac{2}{W_{n}L_{n}} \left[ A_{VTOn}^{2} + \frac{\mu_{p}}{\mu_{n}} A_{VTOp}^{2} \right]$$

a)

$$\sigma_{V_{OS}}^{2} \cong \frac{2}{(0.5\mu)^{2}} \left[ .021^{2} + \frac{1}{3} .025^{2} \right]$$

$$\sigma_{V_{OS}}^{2} \cong 72mV$$

$$3 \sigma_{V_{OS}}^{2} \cong 216mV$$

Note this is a very large offset voltage !

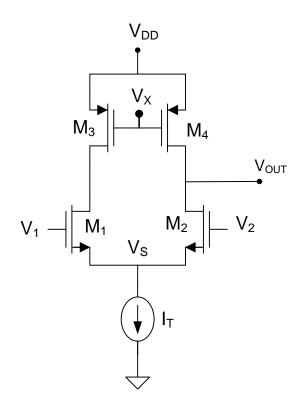

#### Review from Last Lecture Random Offset Voltages

Example: Determine the  $3\sigma$  value of the input offset voltage for The MOS differential amplifier is a) M<sub>1</sub> and M<sub>3</sub> are minimum-sized and b) the area of M<sub>1</sub> and M<sub>3</sub> are 100 times minimum size

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTOn}^{2}}{W_{n}L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n}L_{p}^{2}} A_{VTOp}^{2} \right]$$

$$\sigma_{V_{OS}}^{2} \cong \frac{2}{W_{n}L_{n}} \left[ A_{VTOn}^{2} + \frac{\mu_{p}}{\mu_{n}} A_{VTOp}^{2} \right]$$

$$\sigma_{V_{OS}}^{2} \cong \frac{2}{100(0.5\mu)^{2}} \left[ .021^{2} + \frac{1}{3}.025^{2} \right]$$

$$\sigma_{V_{OS}}^{2} \cong 7.2 \text{mV}$$

$$3 \sigma_{V_{OS}}^{2} \cong 21.6 \text{mV}$$

Note this is much lower but still a large offset voltage !

The area of M<sub>1</sub> and M<sub>3</sub> needs to be very large to achieve a low offset voltage

#### **Random Offset Voltages**

It can be shown that

$$\sigma_{V_{OS}}^{2} \cong 2V_{t}^{2} \left[ \frac{A_{Jn}^{2}}{A_{En}} + \frac{A_{Jp}^{2}}{A_{Ep}} \right]$$

where very approximately

$$A_{Jn} = A_{Jp} = 0.1 \mu$$

#### **Random Offset Voltages**

Example: Determine the  $3\sigma$  value of the offset voltage of a the bipolar input stage if  $A_{E1}=A_{E3}=10\mu^2$

$$\sigma_{V_{OS}}^{2} \cong 2V_{t}^{2} \left[ \frac{A_{Jn}^{2}}{A_{En}} + \frac{A_{Jp}^{2}}{A_{Ep}} \right]$$

$$\sigma_{V_{OS}} \cong \sqrt{2}V_{t} A_{J} \frac{\sqrt{2}}{\sqrt{A_{E}}}$$

$$\sigma_{V_{OS}} \cong 2 \cdot 25 \text{mV} \cdot 0.1 \mu \cdot \frac{1}{\sqrt{10\mu^{2}}} = 1.6 \text{mV}$$

$$3\sigma_{V_{OS}} \cong 4.7 \text{mV}$$

Note this value is much smaller than that for the MOS input structure !

#### **Random Offset Voltages**

Typical offset voltages:

MOS - 5mV to 50MV BJT - 0.5mV to 5mV

These can be scaled with extreme device dimensions

Often more practical to include offset-compensation circuitry

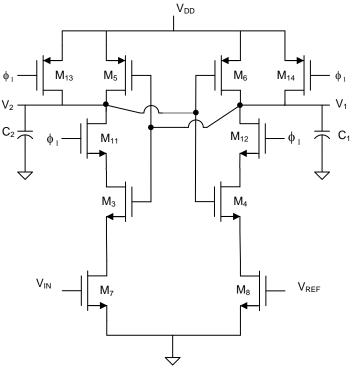

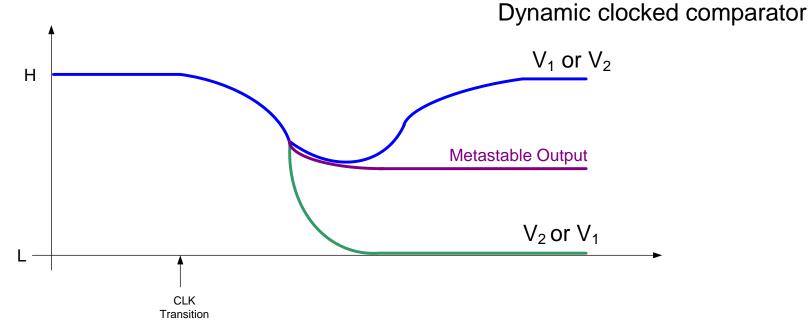

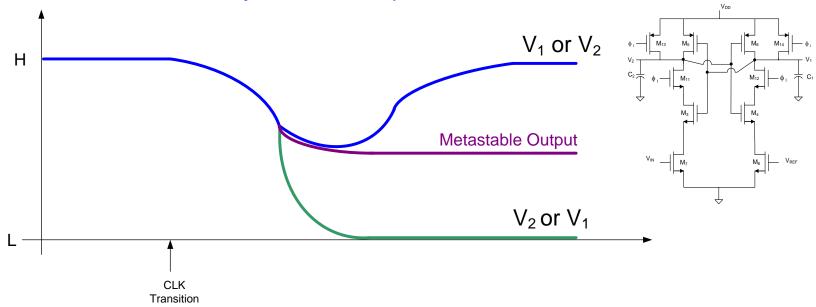

Dynamic Comparators (Regenerative)

Offset voltage difficult to determine in come classes of comparators

Dynamic clocked comparator

- When  $\phi_1$  is low, V<sub>1</sub> and V<sub>2</sub> are precharged to V<sub>DD</sub> and no static power is dissipated

- When  $\phi_1$  is high, enters evaluate state and no static power is dissipated

- Power dissipation almost entirely associated with charging and discharging parasitic capacitors

#### Offset voltage difficult to determine in come classes of comparators

Very small, very fast, low power

But offset voltage can be large (100mV or more)

Decision is being made shortly after clock transition when devices are deep in weak inversion and signal levels are very small

#### **Dynamic Comparators**

Widely used because of low power dissipation

Often include one or more pre-amp stages before regeneration applied

Previous-code dependence and kickback both of concern in dynamic comparators

Noise may significantly affect performance and difficult to analyze and simulate because transient noise models in deep weak inversion are questionable

Still major opportunities to make significant improvement in dynamic comparators

Additional details about offset voltage, statistical circuit analysis, and matching can be found in the draft document

"Statistical Characterization of Circuit Functions" by R.L. Geiger

#### Summary of Offset Voltage Issues

- Random offset voltage is generally dominant and due to mismatch in device

and model parameters

- MOS Devices have large V<sub>OS</sub> if area is small

- $\sigma$  decreases approximately with  $1/\sqrt{A}$

- Multiple fingers for MOS devices offer benefits for common centroid layouts but too many fingers will ultimately degrade offset because perimeter/area ratio will increase (A<sub>W</sub> and A<sub>L</sub> will become of concern)

- Offset voltage of dynamic comparators is often large and analysis not straightforward

- Offset compensation often used when low offsets important

MOS:

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTOn}^{2}}{W_{n}L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n}L_{p}^{2}} A_{VTOp}^{2} \right]$$

Bipolar:

$$\sigma_{V_{OS}}^{2} \cong 2V_{t}^{2} \left[ \frac{A_{Jn}^{2}}{A_{En}} + \frac{A_{Jp}^{2}}{A_{Ep}} \right]$$

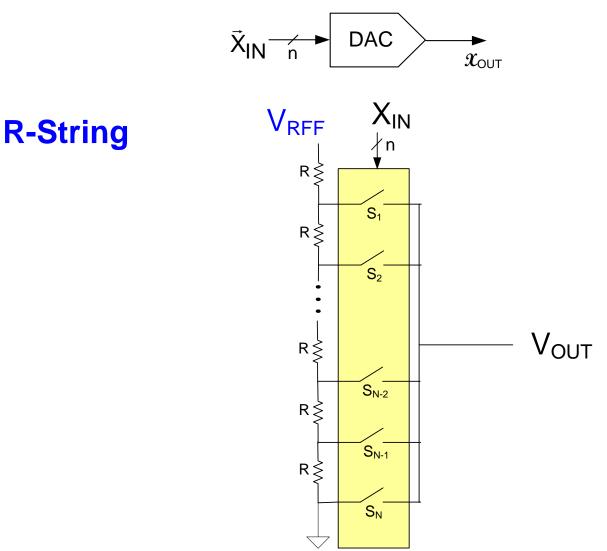

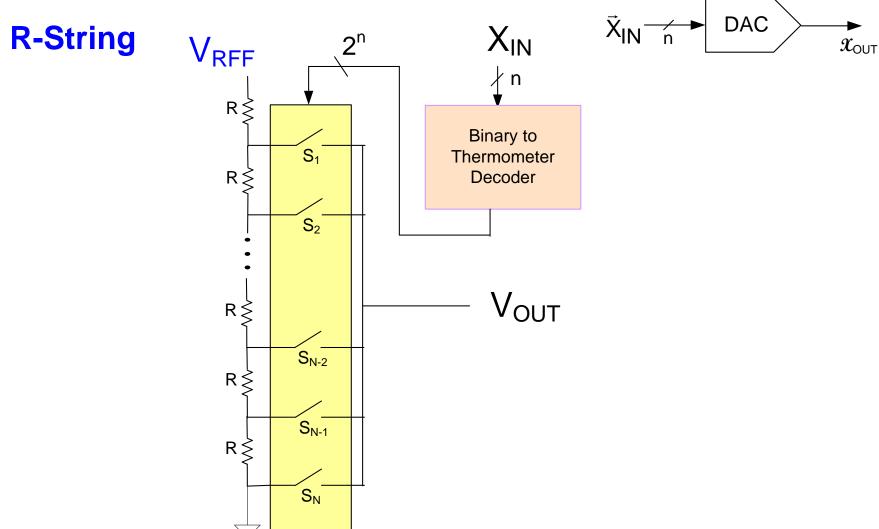

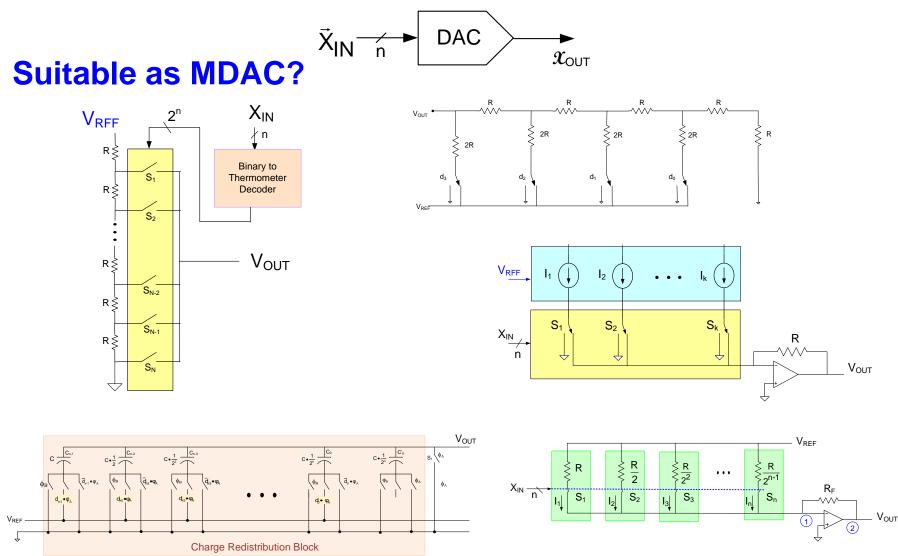

Types (Nyquist Rate)

- Voltage Scaling

- Resistor String DACs (string DACs)

- Interpolating

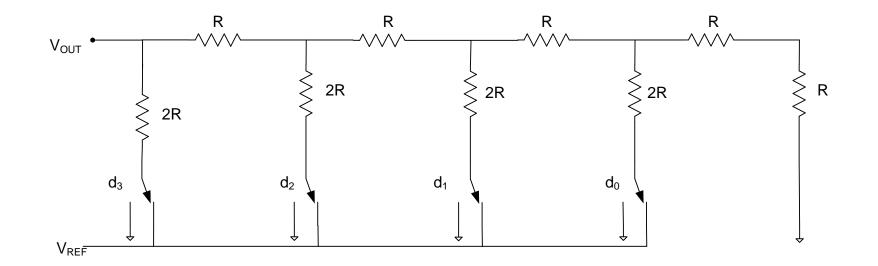

- Current Steering

- Binary Weighted Resistors

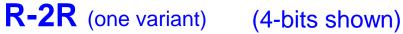

- R-2R Ladders

- Current Source Steering

- Thermometer Coded

- Binary Weighted

- Segmented

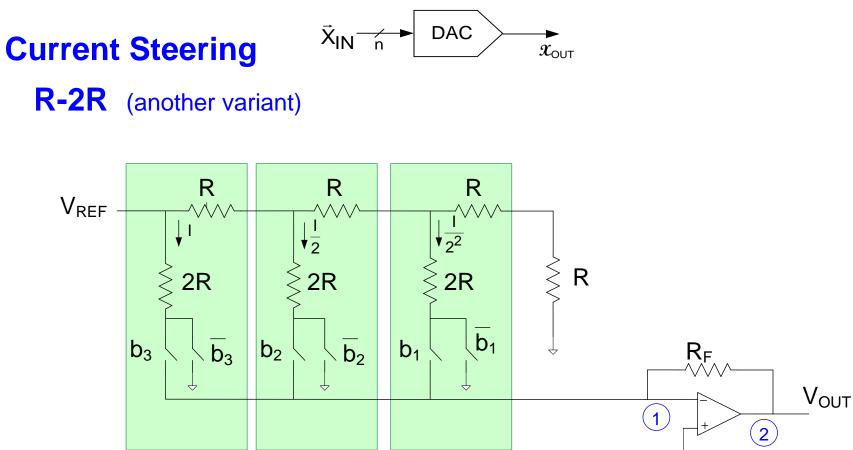

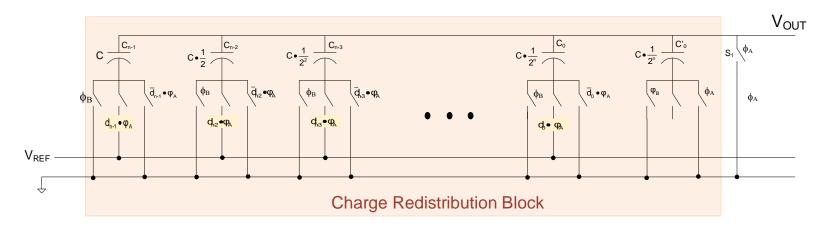

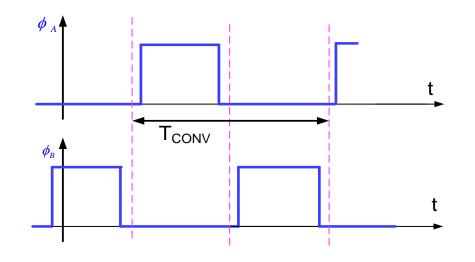

- Charge Redistribution

- Switched Capacitor

- Serial

- Algorithmic

- Cyclic or Re-circulating

- Pipelined

- Integrating

- Resistor Switching

- MDACs (multiplying DACs)

#### Observations

- Yield Loss is the major penalty for not appropriately managing parasitics and matching and this loss can be ruthless

- The ultimate performance limit of essentially all DACs is the yield loss associated with parasitics and matching

- Many designers do not have or use good statistical models that accurately predict data converter performance

- If you work of a company that does not have good statistical device models

- Convince model groups of the importance of developing these models

- (or) develop appropriate test structures to characterize your process

- Existing nonlinear device models may not be sufficiently accurately predict device nonlinearities for high-end data converter applications

#### Structures

- Hybrid or Segmented

- Mode of Operation

- Current Mode

- Voltage Mode

- Charge Mode

- Self-Calibrating

- Analog Calibration

- Foreground

- Background

- Digital Calibration

- Foreground

- Background

- Dynamic Element Matching

- Laser or Link Trimmed

- Thermometer Coded or Binary

- Radix 2 or non-radix 2

- Inherently Monotone

- Type of Classification may not be unique nor mutually exclusive

- Structure is not mutually exclusive

- All approaches listed are used (and probably some others as well)

- Some are much more popular than others

- Popular Architectures

- Resistor String (interpolating)

- Current Source Steering (with segmentation)

- Charge Redistribution

- Many new architectures are possible and some may be much better than the best currently available

- All have perfect performance if parasitic and matching performance are ignored !

- Major challenge is in determining appropriate architecture and managing the parasitics

#### Nonideal Effects of Concern

- Matching

- Parasitic Capacitances (including Charge injection)

- Loading

- Nonlinearities

- Interconnect resistors

- Noise

- Speed

- Jitter

- Temperature Effects

- Aging

- Package stress

#### **Observations**

- Experienced Designers/Companies often produce superior data converter products

- Essentially all companies have access to the same literature, regularly reverse engineer successful competitors products and key benefits in successful competitors products are generally not locked up in patents

- High-end designs( speed and resolution) may get attention in the peer community but practical moderate performance converters usually make the cash flow

- Area (from a silicon cost viewpoint) is usually not the driving factor in high-end designs where attractive price/mfg cost ratios are common

- Considerable ongoing demand for data converter designers particularly in ASICs where DAC optimized for specific application

$X_{IN}$  is decoded to close one switch

**Basic R-String DAC including Logic to Control Switches**

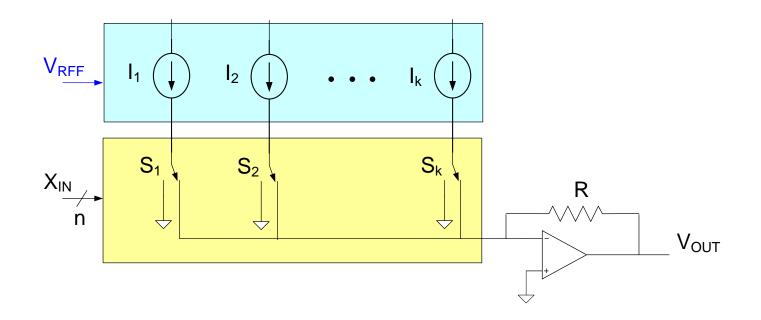

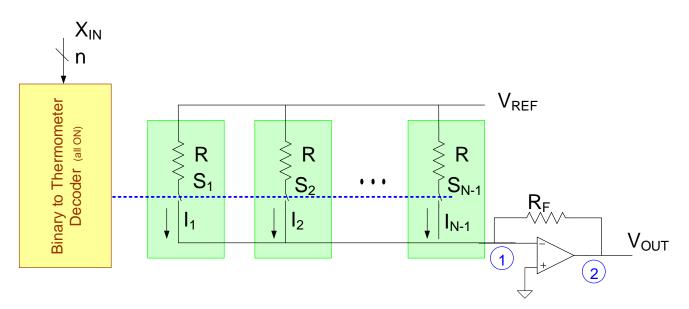

#### **Current Steering**

**Current Steering**

#### Inherently Insensitive to Nonlinearities in Switches and Resistors

- Termed "top plate switching"

- Thermometer coded

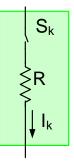

- Based upon unary cell

- Speed limited by Op Amp and clock transients

Unary bit cell

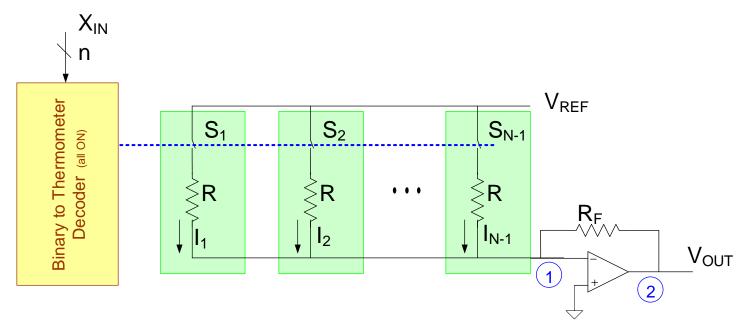

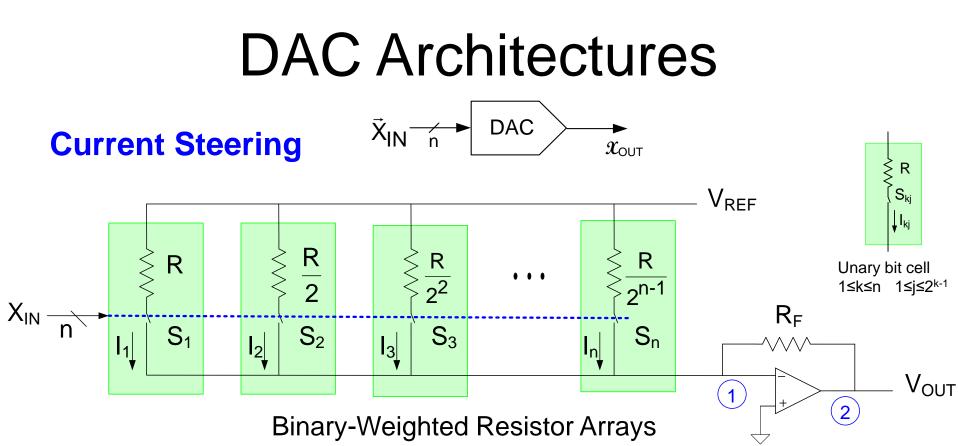

**Current Steering**

#### Inherently Insensitive to Nonlinearities in Switches and Resistors Smaller ON resistance and less phase-shift from clock edges

- Termed "bottom plate switching"

- Thermometer coded

- Based upon unary cell

- Speed limited by Op Amp

- Unary bit cells usually bundled to make resistors

- Same number of unary cells needed as for thermometer coded structure

- Need for decoder eliminated !

- DNL may be a major problem

- INL performance about same as thermometer coded if same unit resistors used

- Sizing and layout of switches is critical

Observe thermometer coding and binary weighted both offer some major advantages and some major limitations

By superposition:

$$V_{OUT} = V_{REF} d_3 \cdot \frac{1}{2} + V_{REF} d_2 \cdot \frac{1}{4} + V_{REF} d_1 \cdot \frac{1}{8} + V_{REF} d_0 \cdot \frac{1}{16} = V_{REF} \sum_{k=0}^{3} \frac{d_k}{2^{4-k}} = V_{REF} \sum_{k=1}^{4} \frac{d_{4-k}}{2^k} = V_{REF} \sum_{k=0}^{4} \frac{d_{4-k}}{2^k} =$$

**R-2R** Resistor Arrays

**Charge Redistribution**  $\vec{X}_{IN} \xrightarrow{n}$

$$Q_{SET} = V_{REF} \sum_{i=0}^{n-1} d_i \frac{C}{2^{n-i}}$$

$$Q_{RDIS} = V_{OUT} \left( \sum_{i=0}^{n-1} C_i + \left[ C_0 \right] \right) = V_{OUT} \left( \sum_{i=0}^{n-1} \frac{C}{2^{n-i}} + \left[ \frac{C}{2^n} \right] \right) = V_{OUT} C$$

$Q_{SET} = Q_{RDIS}$

$$V_{REF} \sum_{i=0}^{n-1} d_i \frac{C}{2^{n-i}} = V_{OUT}C$$

$$V_{OUT} = V_{REF} \sum_{i=0}^{n-1} \frac{d_i}{2^{n-i}}$$

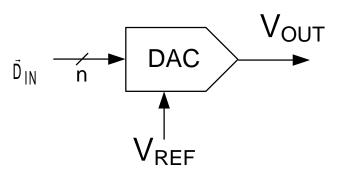

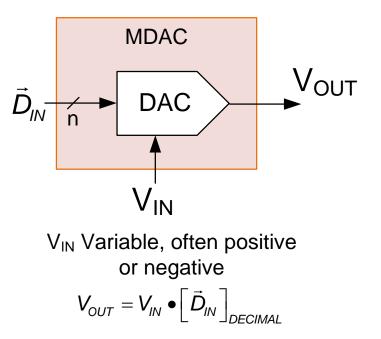

#### **MDAC**

V<sub>REF</sub> fixed or limited range

$$V_{OUT} = V_{REF} \bullet \left[ \vec{D}_{IN} \right]_{DECIMAL}$$

- Some define MDACs to be DAC structures that have current outputs

- Many DAC structures can perform well as a MDAC (possibly one quadrant)

- Performance of some DAC structures limited if V<sub>REF</sub> is varied

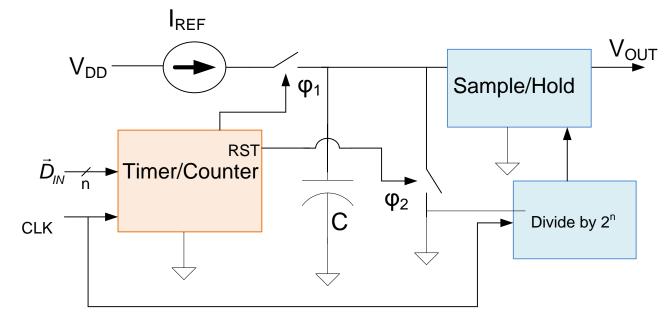

#### Single Slope

Single-Slope DAC

# Stay Safe and Stay Healthy !

### End of Lecture 12